### Four Ports, 2.125 Gbps, 3.3V, 850nm VCSEL, Multimode, Up to 700M Link Distance

#### Key Features & Benefits

- Four independent TX and RX ports at 2.125 Gbps each

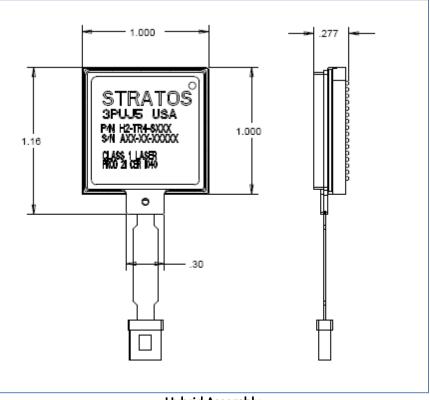

- Small footprint 1.00 inch square

- Low height, less than 0.285 inches max

- Fiber Flex with custom lengths and termini

- BGA socket surface mount, no through holes required

- Removable device (from BGA socket) for IR reflow

- Industrial temp range, vibration tolerant design

- SPI control interface for software control and status

- Control for RX Data Squelch on Loss of Signal

- Control for TX optical Enable/Disable

- Status for RX Signal Detect and Signal Strength

- 3.3V Power, 1.6W max

#### Applications

The H2-TR4-Sxxx Quad Port Hybrid Transceiver provides a highly ruggedized, small footprint, cost effective solution for 1 to 2.5Gbps multimode optical data links. The device includes an integrated Fiber Flex cable terminated into an industry standard 1x12 MT connector. The device may be customized to have different Fiber Flex lengths, custom fiber flex routing, or use alternate types of fiber termini such as ST, SC, or MIL-T-29504. A complete list is provided in the Ordering Options section of this data sheet. These transceivers are designed to operate for 1x/2x Fiber Channel Links, but can be used for any other data communications purpose within their operating parameters, up to 2.5 Gbps per port.

### Product Overview

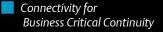

The **Emerson Network Power Connectivity Solutions** H2-TR4-Sxxx Quad Port Hybrid Transceiver consists of a VCSEL and PIN Diode Array, Laser Driver, Post Amp circuits, a microcontroller, and integrated fiber flex with MT termination. The electrical signals are routed through a BGA surface mount pin/socket connector to allow easy removal of the entire assembly and to support BGA reflow thermal profiles for ease of PCB assembly. The transmitter accepts four sets of differential data and drives a quad 850nm VCSEL array. The VCSEL drive circuit includes a temperature sensor circuit to

### Ordering Information

H2 - TR4 - Sxxx The –Sxxx suffix represents unique part numbering for fiber route and termini options. See page 22 or consult the factory for details and for custom part numbering for your application.

drive temperature compensation of the optical output level in order to maintain stable output power level over the thermal range. The internal microprocessor provides software control for each individual transmit port for TX Enable/Disable and TX diagnostics. The receiver uses a quad 850nm GaAs PIN array, post amplifier, and outputs four sets of differential data. The internal microprocessor enables software control or read for individual port RX Signal Detect, RX Squelch enable/disable, and Receive Signal Strength Indicators (RSSI). The data interface for the device is a  $100\Omega$ differential pair,  $50\Omega$  impedance per line, and is CML compliant. Individual LVTTL hardware status pins are provided for RX Signal Detect, RX Enable, TX Enable, and TX Fault. The hardware control allows an FPGA or other hardware device to control and monitor the main functions of the Hybrid Transceiver. Software control is provided using a Serial Peripheral Interface (SPI) 4-wire bus. The SPI bus operates in a bit-serial fashion at clock rates up to 2MHz. The internal registers are addressed through a 3 byte read or write sequence. The control and status of the device via software is not required for operation, and is provided purely as an enhancement to operation. The Power Up default SPI register values are all configured for normal operation on all channels, thereby allowing the transceiver's control pins to configure the device without any SPI activity.

Connectivity for

Business Critical Continuity

#### **BGA Socket Operation**

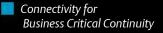

The H2-TR4-Sxx Quad Port Hybrid Transceiver uses a surface mount micro BGA socket, which is constructed of high temp G-11 material and houses an array of socket contacts. The BGA socket is soldered to the application card through normal IR or Thermal oven reflow cycles. There are not any through-hole pins, allowing the device to be used in solid core-board type applications. The actual transceiver device, which contains the active circuits, optics, and Fiber Flex pigtail, has an array of pins located on the bottom of the device that insert into the surface mount BGA socket. The transceiver is inserted into the BGA socket with approximately 15 pounds of force. The entire structure consisting of the BGA socket and the transceiver device fits within 0.285 inch maximum height. The transceiver is removed by using a pull tool to lift the transceiver pins from the BGA socket. The entire structure is designed to withstand avionics vibration and shock requirements, yet allow ease of manufacturing and re-work.

#### Absolute Maximum Ratings

Absolute maximum limits mean that no catastrophic damage will occur if the product is subjected to these ratings for short periods, provided each limiting parameter is in isolation and all other parameters have values within the performance specification. It should not be assumed that limiting values of more than one parameter can be applied to the product at the same time.

| Parameter                        | Symbol            | MIN  | Typical | MAX             | Unit    |

|----------------------------------|-------------------|------|---------|-----------------|---------|

| Storage Temperature              | Ts                | -55  |         | +125            | °C      |

| BGA Socket Soldering Temperature | T <sub>SOLD</sub> |      |         | +270            | °C      |

| Lead Soldering Time              | t <sub>solD</sub> |      |         | 10              | Seconds |

| Supply Voltage                   | V <sub>cc</sub>   | -0.5 |         | +3.6            | V       |

| Data Input Voltage               | V <sub>I</sub>    | -0.5 |         | V <sub>cc</sub> | V       |

| Differential Input Voltage (p-p) | V <sub>D</sub>    |      |         | 2.2             | V       |

### **Recommended Operating Conditions**

| Parameter                                      | Symbol          | MIN             | Typical | MAX             | Unit |

|------------------------------------------------|-----------------|-----------------|---------|-----------------|------|

| Operating Temperature Limit – Case             | T <sub>c</sub>  | -40             |         | +85             | °C   |

| Storage Temperature – Long Term                | Τ <sub>s</sub>  | -40             |         | +100            | °C   |

| Supply Voltage                                 | V <sub>cc</sub> | +3.135          |         | +3.465          | V    |

| Differential Data Output Voltage Swing (p-p)   | V <sub>DO</sub> | 300             |         | 800             | mV   |

| Differential Data Input Voltage Swing (p-p)    | V <sub>DI</sub> | 200             |         | 800             | mV   |

| Differential Data Impedance                    | Z               | 80              | 100     | 120             | Ω    |

| Differential Data Impedance, Single Ended      | RL              |                 | 50      |                 | Ω    |

| Control Signal Input Voltage High              | V <sub>IH</sub> | 2.2             |         | V <sub>cc</sub> | V    |

| Control Signal Input Voltage Low               | V <sub>IL</sub> | V <sub>EE</sub> |         | 0.5             | V    |

| Status Signal Output Voltage High <sup>1</sup> | V <sub>OH</sub> | 2.4             |         | V <sub>cc</sub> | V    |

| Status Signal Output Voltage Low <sup>2</sup>  | V <sub>OL</sub> | V <sub>EE</sub> |         | 0.4             | V    |

| Supply Current                                 | I <sub>cc</sub> | 200             |         | 400             | mA   |

1. Current Output High (loh) = -10.0mA max

2. Current Output Low (lol) = 8.5mA max

Connectivity for Business Critical Continuity

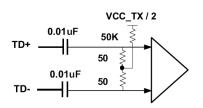

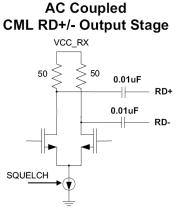

Detail of Data I/O Stages AC Coupled CML Input Stage

#### **Transmitters:** VCCTX = 3.135V to 3.465V, T<sub>A</sub> = Operating Temperature Range

| Parameter                                   | Symbol                | MIN  | Typical | MAX  | Unit  |

|---------------------------------------------|-----------------------|------|---------|------|-------|

| Optical Output <sup>1</sup>                 | Po                    | -6.0 | -3.0    | -0.5 | dBm   |

| Optical Output Wavelength                   | $\lambda_{OUT}$       | 830  | 850     | 860  | nm    |

| Spectral Width                              | $\Delta\lambda_{RMS}$ |      |         | 0.85 | nm    |

| Extinction Ratio                            | ER                    | 7    | 9       |      | dB    |

| Total Jitter (TX contribution, p-p)         | Tj                    |      |         | 114  | psec  |

| Deterministic Jitter (TX contribution, p-p) | Dj                    |      |         | 56   | psec  |

| Relative Intensity Noise                    | RIN                   |      |         | -117 | dB/Hz |

| Optical Modulation Amplitude (p-p)          | OMA                   | 196  |         |      | μW    |

1. BER=10<sup>-12</sup> @ 2.125 GigaBaud, PRBS = 2<sup>7</sup>-1, NRZ

#### **Receivers:** VCCTX = 3.135V to 3.465V, T<sub>A</sub> = Operating Temperature Range

|                                             | <u> </u>          |       |         |       |      |

|---------------------------------------------|-------------------|-------|---------|-------|------|

| Parameter                                   | Symbol            | MIN   | Typical | MAX   | Unit |

| Optical Sensitivity <sup>1,2</sup>          | P                 | -16.0 | -18.0   |       | dBm  |

| Receiver Saturation                         | P <sub>SAT</sub>  |       |         | 0.0   | dBm  |

| Optical Wavelength                          | $\lambda_{IN}$    | 830   |         | 860   | nm   |

| Optical Modulation Amplitude <sup>1,2</sup> | OMA               | 36.5  | 25      |       | μW   |

| Signal Detect Assert Time                   | t <sub>sDAS</sub> |       | <10     | 100   | μS   |

| Signal Detect Deassert Time                 | t <sub>sdda</sub> |       | <10     | 350   | μS   |

| Signal Detect Deassert Level <sup>3</sup>   | SD <sub>OFF</sub> | -26.5 |         |       | dBm  |

| Signal Detect Assert Level                  | SD <sub>ON</sub>  |       |         | -16.5 | dBm  |

| Signal Detect Hysteresis                    | HYS               | 1.0   | 2.0     | 3.0   | dB   |

| Total Jitter (RX contribution, p-p)         | Tj                |       |         | 150   | psec |

| Deterministic Jitter (RX contribution, p-p) | Dj                |       |         | 47    | psec |

1. BER=10<sup>-12</sup> @ 2.125 GigaBaud, PRBS = 2<sup>7</sup>-1, NRZ

2. Assuming an Extinction Ratio of 8dB or higher

3. RX data outputs are squelched when Signal Detect is deasserted to prevent noise data output when no optical signal is present

Connectivity for Business Critical Continuity

### Link Distances

| Fiber Specification | Application                  | Distance |

|---------------------|------------------------------|----------|

| 50/125 (4700MHz*Km) | 2X Fiber Channel (2.125Gbps) | 700M     |

Fiber type: Corning OM4 50/125/245 Multimode Fiber

#### **Regulatory Compliance**

| Requirement           | Feature    | Condition        | Notes                               |

|-----------------------|------------|------------------|-------------------------------------|

| MIL-STD-883-3015.7    | ESD        | Class II         | 2200V                               |

| IEC-801-2             | ESD        | Human Body Model | 25KV                                |

| IEC-801-3             | EMI        | Immunity         | 10V/M                               |

| FCC                   | EMI        | Class B          | >20dB                               |

| EN 55022 (CISPR 22A)  | EMI        | Class B          | 10V/M                               |

| IEC-825 Issue 1993-11 | Eye Safety | Class 1          | TUV Certificate Number – In Process |

| FDA CDRH 21-CFR 1040  | Eye Safety | Class 1          | CDRH Accession Number – In Process  |

Connectivity for Business Critical Continuity

|          |          |          | B        | BGA Pi   | in-Ou    | t, App   | licati | on Ca | rd Foo | otprin   | it, Top  | o View | /        |          |           |    |

|----------|----------|----------|----------|----------|----------|----------|--------|-------|--------|----------|----------|--------|----------|----------|-----------|----|

| Q        | Ρ        | 0        | Ν        | Μ        | L        | Κ        | J      | Н     | G      | F        | Е        | D      | С        | В        | А         |    |

| GND      | GND      | GND      | S<br>CLK | S<br>CSX | SIN      | S<br>OUT | NC     | NC    | GND    | RX<br>EN | NC       | GND    | NC       | NC       | GND       | 1  |

| GND      | GND    | GND   | GND    | GND      | GND      | GND    | GND      | GND      | NC        | 2  |

| GND      | GND      | GND      | VDD      | VDD      | VDD      | GND      | GND    | GND   | GND    | VDD      | VDD      | VDD    | VDD      | GND      | NC        | 3  |

| NC       | GND      | VDD      | VDD      | VDD      | VDD      | GND      | GND    | GND   | GND    | VDD      | VDD      | VDD    | VDD      | GND      | SQ<br>EN  | 4  |

| RST      | GND      | VDD      | VDD      |          |          |          |        |       |        |          |          | VDD    | VDD      | GND      | RX<br>SD3 | 5  |

| TX<br>EN | GND      | VDD      | VDD      |          |          |          |        |       |        |          |          | VDD    | VDD      | GND      | RX<br>SD2 | 6  |

| NC       | GND      | GND      | GND      |          |          | GND      | GND    | GND   | GND    |          |          | GND    | GND      | GND      | RX<br>SD1 | 7  |

| RDY      | GND      | GND      | GND      |          |          | GND      | GND    | GND   | GND    |          |          | GND    | GND      | GND      | RX<br>SD0 | 8  |

| FLT      | GND      | GND      | GND      |          |          | GND      | GND    | GND   | GND    |          |          | GND    | GND      | GND      | NC        | 9  |

| GND      | GND      | VDD      | VDD      |          |          | GND      | GND    | GND   | GND    |          |          | VDD    | VDD      | GND      | GND       | 10 |

| TD0<br>- | GND      | VDD      | VDD      |          |          |          |        |       |        |          |          | VDD    | VDD      | GND      | RD0<br>+  | 11 |

| TD0<br>+ | GND      | VDD      | VDD      |          |          |          |        |       |        |          |          | VDD    | VDD      | GND      | RD0<br>-  | 12 |

| GND      | GND      | VDD      | VDD      | GND      | GND      | GND      | GND    | GND   | GND    | GND      | GND      | VDD    | VDD      | GND      | GND       | 13 |

| TD1<br>- | GND      | VDD      | VDD      | GND      | GND      | GND      | GND    | GND   | GND    | GND      | GND      | VDD    | VDD      | GND      | RD1<br>+  | 14 |

| TD1<br>+ | GND      | GND      | GND      | GND      | GND      | GND      | GND    | GND   | GND    | GND      | GND      | GND    | GND      | GND      | RD1<br>-  | 15 |

| GND      | TD2<br>- | TD2<br>+ | GND      | TD3<br>- | TD3<br>+ | GND      | GND    | GND   | GND    | RD3<br>- | RD3<br>+ | GND    | RD2<br>- | RD2<br>+ | GND       | 16 |

EMERSON. Network Power

**Stratos** Connectivity Solutions

#### Pin Functions – Power and Ground

| Pin Number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Symbol | Description                           | Logic Family |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------------------------------------|--------------|

| A1, D1, G1, O1, P1, Q1, Q2, Q3, A10, Q10,<br>A13, Q13, A16, D16, G16, H16, J16, K16, N16, Q16,<br>B2, C2, D2, E2, F2, G2, H2, J2, K2, L2, M2, N2, O2, P2,<br>B3, G3, H3, J3, K3, O3, P3, B4, G4, H4, J4, K4, P4,<br>B5, P5, B6, P6, B7, C7, D7, G7, H7, J7, K7, N7, O7, P7,<br>B8, C8, D8, G8, H8, J8, K8, N8, O8, P8,<br>B9, C9, D9, G9, H9, J9, K9, N9, O9, P9,<br>B10, G10, H10, J10, K10, P10, B11, P11,<br>B12, P12, B13, E13, F13, G13, H13, J13, K13, L13, M13, P13,<br>B14, E14, F14, G14, H14, J14, K14, L14, M14, P14,<br>B15, C15, D15, E15, F15, G15, H15, J15, K15, L15,<br>M15, N15, O15, P15 | GND    | Power and Signal<br>Return, 500mA max | GND          |

| C3, D3 C12, D12, C13, D13,<br>C14, D14, C4, D4, C5, D5,<br>N12, O12, N13, O13, N14,<br>O14, N3, N4, O4, N5, O5,<br>E3, F3, E4, F4, C6, D6,<br>C10, D10, C11, D11, L3, M3,<br>L4, M4, N6, O6, N10, O10,<br>N11, O11                                                                                                                                                                                                                                                                                                                                                                                          | VDD    | 3.3VDC Power,<br>200mA max            | POWER        |

### Pin Functions – Transmitter Data and H/W Control

| Pin Number | Symbol             | Direction | Description                                                                                                                                                                                       | Logic Family |

|------------|--------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| Q12, Q11   | TD0+, TD0-         | I         | Differential TX Data, Channel 0                                                                                                                                                                   | CML          |

| Q15, Q14   | TD1+, TD1-         | 1         | Differential TX Data, Channel 1                                                                                                                                                                   | CML          |

| O16, P16   | TD2+, TD2-         | I         | Differential TX Data, Channel 2                                                                                                                                                                   | CML          |

| L16, M16   | TD3+, TD3-         | 1         | Differential TX Data, Channel 3                                                                                                                                                                   | CML          |

| Q6         | TXEN <sup>1</sup>  | I         | TX Enable, All Channels<br>(1=Enable, 0=Disable, 4.7KΩ internal pull-up)                                                                                                                          | LVTTL        |

| Q9         | FAULT <sup>2</sup> | 0         | TX Fault Status<br>(1=Fault, 0=No Fault)                                                                                                                                                          | LVTTL        |

| Q8         | RDY <sup>3</sup>   | 0         | Power Up Reset operation complete, Self Tests<br>complete, Ready for Normal operation, rising edge of<br>RDY will occur within 100msec of Power-up or rising<br>edge RESET. (Rising Edge = Ready) | LVTTL        |

1. TXEN also requires the SPI register TXEN to be in the enable state before ENABLE condition is achieved

2. FAULT is set or cleared as a summary fault condition of the VCSEL. The individual channel faults are available via the SPI registers

3. RDY will assert 1 at RESET or powers up followed by deassert 0 approx. 55ms later. The subsequent rising edge of RDY indicates completion of the device initialization sequence.

Connectivity for Business Critical Continuity

Connectivity for Business Critical Continuity

### Pin Functions – Receiver Data and H/W Control

| Pin Number | Symbol             | Direction | Description                                                                           | Logic Family |

|------------|--------------------|-----------|---------------------------------------------------------------------------------------|--------------|

| A11, A12   | RD0+, RD0-         | 0         | Differential RX Data, Channel 0                                                       | CML          |

| A14, A15   | RD1+, RD1-         | 0         | Differential RX Data, Channel 1                                                       | CML          |

| B16, C16   | RD2+, RD2-         | 0         | Differential RX Data, Channel 2                                                       | CML          |

| E16, F16   | RD3+, RD3-         | 0         | Differential RX Data, Channel 3                                                       | CML          |

| A8         | RXSD0 <sup>1</sup> | 0         | RX Signal Detect, Channel 0<br>(1=Input Optical Signal Detected, 0=No Signal)         | LVTTL        |

| A7         | RXSD1 <sup>1</sup> | 0         | RX Signal Detect, Channel 1<br>(1=Input Optical Signal Detected, 0=No Signal)         | LVTTL        |

| A6         | RXSD2 <sup>1</sup> | 0         | RX Signal Detect, Channel 2<br>(1=Input Optical Signal Detected, 0=No Signal)         | LVTTL        |

| A5         | RXSD3 <sup>1</sup> | 0         | RX Signal Detect, Channel 3<br>(1=Input Optical Signal Detected, 0=No Signal)         | LVTTL        |

| A4         | SQEN               | I         | Squelch Enable, All Channels<br>(1=Squelch Enable, 0=Disable, 4.7KΩ internal pull-up) | LVTTL        |

| F1         | RXEN <sup>2</sup>  | I         | RX Enable, All Channels<br>(1=Enable, 0=Disable, 4.7KΩ internal pull-up)              | LVTTL        |

1. The RXSDx status pins are valid only if the RXEN H/W pin and SPI resisters are in the ENABLE state (=1). If the receiver is in the DISABLE state, then the RXSDx lines are driven HI (=1).

2. RXEN also requires the SPI register RXEN to be in the enable state before ENABLE condition is achieved.

### Pin Functions – S/W Control, Emulator, Test Points, N/C

| Pin #                                         | Symbol | Direction | Description                                                                                                                                                                              | Logic |

|-----------------------------------------------|--------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| L1                                            | SIN    | l         | SPI Port Data In                                                                                                                                                                         | LVTTL |

| K1                                            | SOUT   | 0         | SPI Port Data Out                                                                                                                                                                        | LVTTL |

| N1                                            | SCLK   |           | SPI Clock                                                                                                                                                                                | LVTTL |

| M1                                            | SCSX   | I         | SPI Port Chip Select<br>(0=Select, 1=Not Selected, internal 4.7KΩ pull-up)                                                                                                               |       |

| Q5                                            | RESET  | I/O       | Low True Reset with internal 4.7K pull-up. Also<br>used for Emulator Clock. The minimum pulse low<br>to activate RESET is 20usec.                                                        | LVTTL |

| Q7, E1, Q4,<br>J1, H1, A2, A3,<br>B1, C1, A9, | N/C    | N/C       | These pins allow this device to remain footprint<br>complaint with the previous Hybrid Transceiver<br>design HTP-TR4-S1xx.<br>The pins are recommended for No Connect on new<br>designs. | N/C   |

Connectivity for Business Critical Continuity

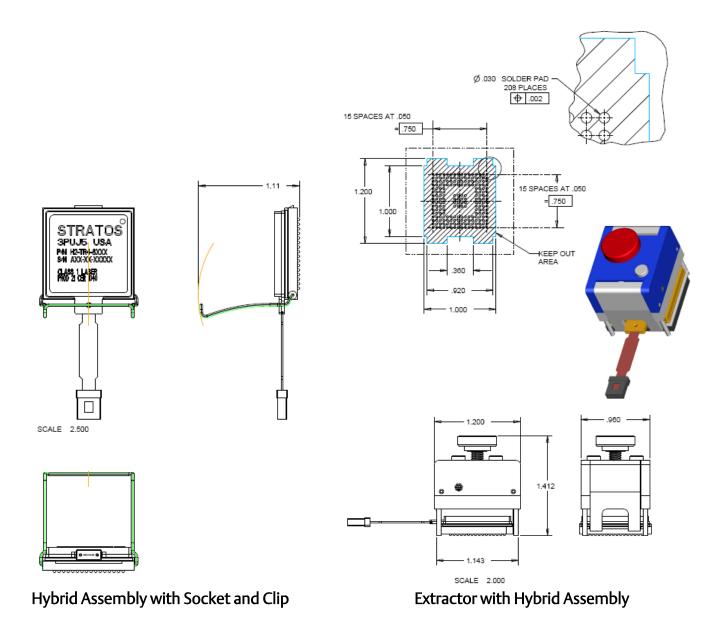

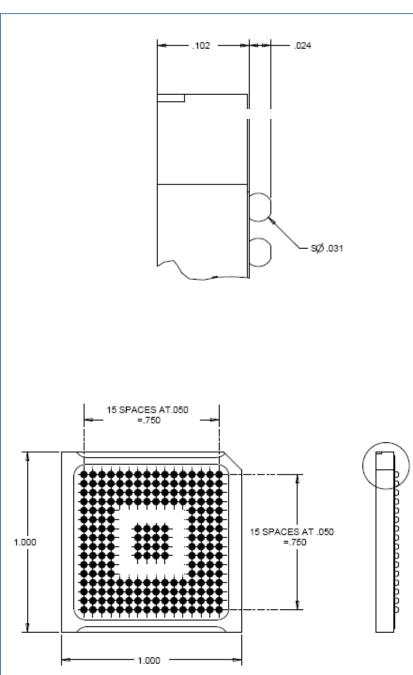

Hybrid Assembly All dimensions ± .005 unless noted

### **BGA Socket Detail\***

| Value                                                   |

|---------------------------------------------------------|

| 50 micron Gold over 100 micron Nickel                   |

| 16x16, 1.27mm spacing                                   |

| 0.036 inch diameter                                     |

| 208                                                     |

| 15 pounds initial, 7 pounds subsequent insertions       |

| 7 pounds                                                |

| 100 cycles minimum                                      |

| 235 C for 2 seconds, do not exceed 270 C for 10 seconds |

|                                                         |

\* See page 23 for mechanical detail.

Connectivity for Business Critical Continuity

**Stratos** Connectivity Solutions

Connectivity for Business Critical Continuity

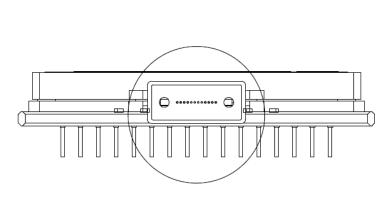

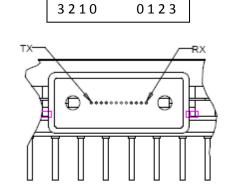

### Straight Route Detail of MT Fiber Connector

#### Straight Route MT12 Fiber Connector Optical Signal Description

| Pin Number | Symbol | Direction | Description          |  |  |

|------------|--------|-----------|----------------------|--|--|

| F1         | TX0    | 0         | Optical TX Channel 0 |  |  |

| F2         | TX1    | 0         | Optical TX Channel 1 |  |  |

| F3         | TX2    | 0         | Optical TX Channel 2 |  |  |

| F4         | TX3    | 0         | Optical TX Channel 3 |  |  |

| F5         | N/C    |           | Reserved for Future  |  |  |

| F6         | N/C    |           | Reserved for Future  |  |  |

| F7         | N/C    |           | Reserved for Future  |  |  |

| F8         | N/C    |           | Reserved for Future  |  |  |

| F9         | RX3    |           | Optical RX Channel 3 |  |  |

| F10        | RX2    |           | Optical RX Channel 2 |  |  |

| F11        | RX1    |           | Optical RX Channel 1 |  |  |

| F12        | RX0    |           | Optical RX Channel 0 |  |  |

Direction O = Output from the optical transceiver Direction I = Input to the optical transceiver MT12 Fiber is 50/125 micron multimode

Connectivity for Business Critical Continuity

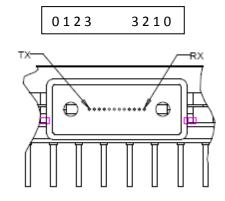

Optional Shuffle Route Detail of MT Fiber Connector

### Shuffle Route MT12 Fiber Connector Optical Signal Description

| Pin Number | Symbol | Direction                        | Description                      |  |

|------------|--------|----------------------------------|----------------------------------|--|

| F1         | TX3    | 0                                | Optical TX Channel 3             |  |

| F2         | TX2    | 0                                | Optical TX Channel 2             |  |

| F3         | TX1    | 0                                | Optical TX Channel 1             |  |

| F4         | TX0    | 0                                | Optical TX Channel 0             |  |

| F5         | N/C    |                                  | Reserved for Future TX Channel 5 |  |

| F6         | N/C    |                                  | Reserved for Future TX Channel 4 |  |

| F7         | N/C    | Reserved for Future RX Channel 4 |                                  |  |

| F8         | N/C    |                                  | Reserved for Future RX Channel 5 |  |

| F9         | RX0    |                                  | Optical RX Channel 0             |  |

| F10        | RX1    |                                  | Optical RX Channel 1             |  |

| F11        | RX2    |                                  | Optical RX Channel 2             |  |

| F12        | RX3    |                                  | Optical RX Channel 3             |  |

Direction O = Output from the optical transceiver Direction I = Input to the optical transceiver MT12 Fiber is 50/125 micron multimode

Connectivity for Business Critical Continuity

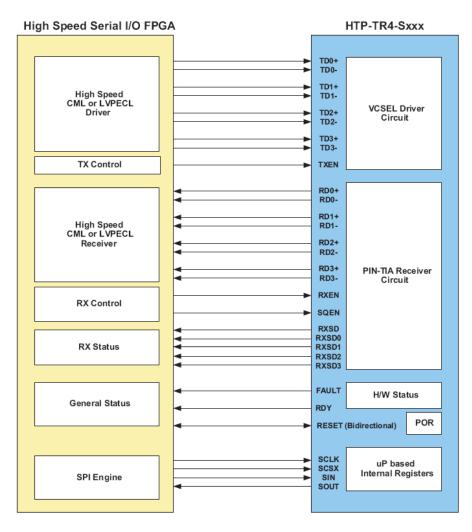

### **Application Block Diagram**

Notes:

- 1. High speed TDX+/- and RDX+/- signals are CML compliant, AC coupled, and will work with either CML or LVPECL driver/receiver logic in the FPGA.

- 2. Keep high speed data signals routed using proper  $50\Omega$  impedance,  $100\Omega$  differential routes, taking care to keep both signals in the differential pair at same trace length.

- 3. The RESET signal is bidirectional, and may be driven by the Power On Reset (POR) circuit in response to a brown out condition detected on the internal Power Supply Monitor.

- 4. The SPI bus may be multiple slaves, with SCLK continuously running, and SCSX used to select those transactions for this particular device.

Connectivity for Business Critical Continuity

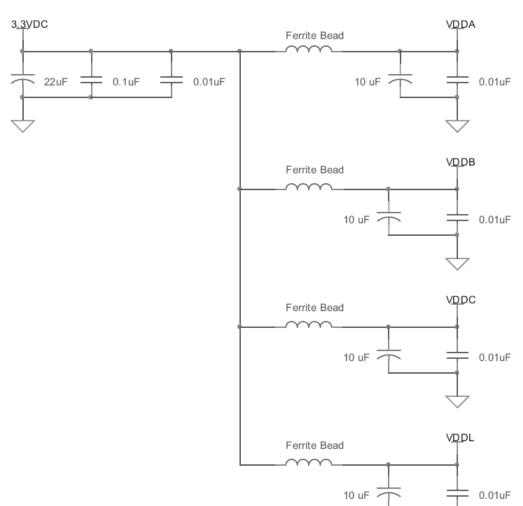

### **Recommended Power Supply Filtering**

Notes:

- 1. Ferrite Bead recommendation MuRata BLM21A601S, provide  $600\Omega$  at 100MHz or better.

- 2. Place 10uF and 0.01uF capacitors as close as practical to the associated power pins on the device.

Connectivity for Business Critical Continuity

| Stratos<br>H2-TR4-Sxxx<br>Hybrid Technology Quad Optical Transceiver                                                        | Connectivity for<br>Business Critical Continuity   |

|-----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

|                                                                                                                             |                                                    |

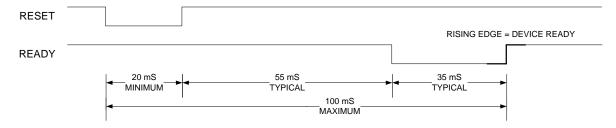

| Power Up, Reset, Ready, and Fault Operation<br>The Hybrid Transceiver contains an internal Power Supply monitor circuit, wh | hich will hold the device in RESET until the power |

The Hybrid Transceiver contains an internal Power Supply monitor circuit, which will hold the device in RESET until the power conditions are acceptable (about 2.7V). At this time, the Power On Reset circuit will release the RESET and allow the Hybrid Transceiver to initialize. The RESET is open collector, and the application card may continue to hold RESET low until some future time.

Once RESET is released by all sources, the Hybrid Transceiver will perform an internal self-test and then initialize for power-up default operation. The READY pin will be driven true (=1) following the rising edge of RESET. Approximately 55 mS later the READY pin will be driven low (=0) for approximately 35 mS. The subsequent *rising edge* of READY pin is the indication that the device is ready for data and SPI port communications. The maximum time from rising edge RESET to rising edge READY condition is 100msec.

After READY is issued, the Hybrid Transceiver will monitor the transceiver for TX VCSEL fault conditions. If any of the enabled TX channels have a VCSEL fault, the Hybrid Transceiver will issue a FAULT status for both the H/W pin and in the internal SPI register. Operation continues as normal. The H/W FAULT status is removed once the VCSEL fault condition clears. A latched version of the fault status is kept in the SPI register and is reset upon read.

### Channel Enable/Disable, Squelch, and Signal Detect Operation

Once the Power up and Self Test operations are complete, the Hybrid Transceiver is ready for normal operation. The TX and RX channels are enabled or disabled through both H/W and SPI register settings. To enable the TX operation, the TXEN H/W pin must be controlled to the ENABLE state, and the internal SPI register TXEN must be configured for each enables channel. It is possible to enable/disable individual channels through the SPI register TXEN settings. When a TX channel is DISABLED, the associated circuitry is powered down within the Hybrid Transceiver within 10msec. Upon ENABLE control via the H/W pin or SPI register control, the associated TX channel will resume normal operation within 10msec.

To enable the RX operation, the RXEN H/W pin must be controlled to the ENABLE state, and the internal SPI register RXEN must be configured for each enabled channel. It is possible to enable/disable individual channels through the SPI register RXEN settings. When an RX channel is DISABLED, the associated circuitry is powered down within the Hybrid Transceiver within 10msec. Upon ENABLE control via the H/W pin or SPI register control, the associated RX channel will resume normal operation within 10msec. If the RX channel is DISABLED the RX Data output signals will be turned off (AC coupled, no transitions).

In many systems, it is desirable to squelch the RX data to a known state whenever the RX optical signal is lost, in order to prevent random noise data from propagating through the system. The Hybrid Transceiver may be configured to squelch the RX data on loss of signal by controlling the H/W SQEN pin. This function is under H/W control only; there is not a corresponding SPI register to control the SQEN state. If the Hybrid Transceiver is configured for SQEN, the RX Data output signals will be

Connectivity for Business Critical Continuity

turned off (AC coupled, no transitions) if the optical signal is not detected. The SQEN control affects all RX channels; there is not an individual control for each RX channel.

The Hybrid Transceiver will monitor the RX optical signal and issue a Signal Detect status on each individual channel is a valid modulated optical signal is detected. The RXSD status is available through both H/W status pins and SPI registers. There is also a summary H/W Signal Detect RXSD pin representing the wire-OR of the individual RXSD0 through RXSD3 status. The RXSD and RXSD0 through RXSD3 H/W pin status are valid only if the receiver channel is ENABLED (via the H/W pin and SPI registers).

The Hybrid Transceiver will monitor the incoming TX Data activity on each individual channel. If data is detected on the incoming TX Data lines, the corresponding status bit will be set in the TXSD SPI register. There is not a corresponding H/W status pin for this function. The TXSD test circuit is after the TD+/- differential receiver, therefore the logic cannot be used to detect a fault on a single leg TD+ or TD- by itself. The application card may choose to test each individual leg in isolation and check for TXSD condition as a diagnostic test.

#### **SPI Port Operation**

The Hybrid Transceiver can be controlled through the SPI bus interface, in order to allow S/W configuration and control for several parameters. The Transceiver register map and theory of operation is presented in this section. Timing and SPI waveforms are presented in the following section.

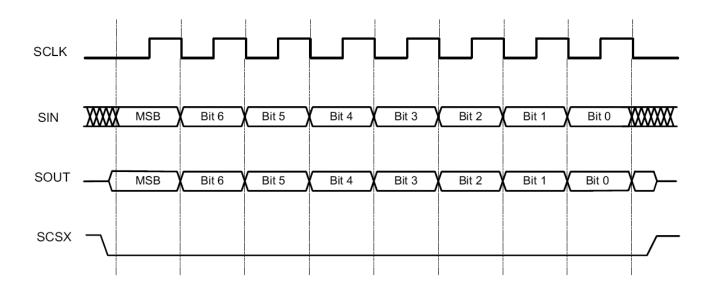

The SPI interface is a 4 wire bus with Chip Select (SCSX), Serial Data In (SIN), Serial Data Out (SOUT), and Serial Clock (SCLK). The device operates in the slave mode, so the SCLK, SIN, and SCSX are always inputs (data to the Hybrid Transceiver), and SOUT is always a tri-stateable output (data from the Hybrid Transceiver). Data is transmitted and received Most Significant Bit (MSB) first.

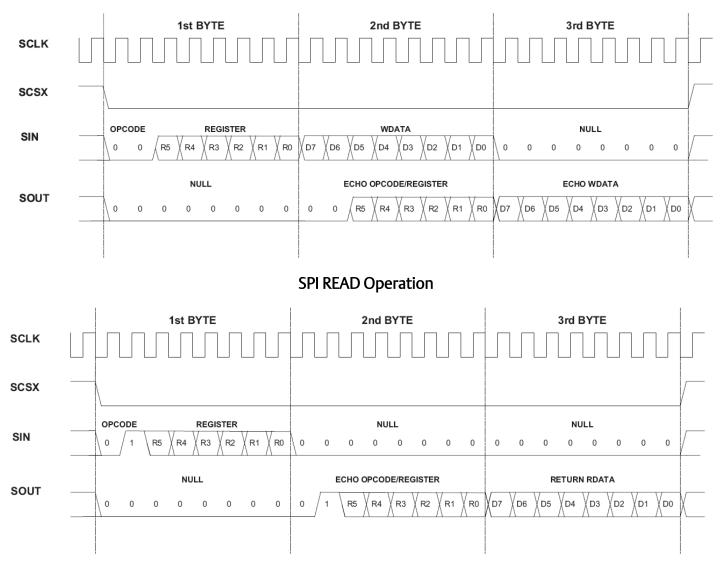

#### SPI Op Code

The SPI operation is initiated by the SPI Master by driving SPI Chip Select low (SCSX = 0). All transfers are 3 bytes long. The first byte contains the Op Code (Most Significant 2 bits) and Register Address (Least Significant 6 bits). The MSB byte aligned Op Code value may be 0x40 (READ) or 0x00 (WRITE). All other op codes (0xc0 and 0x80) will result in no operation. Once the Op Code/Register Address byte is received, the Hybrid Transceiver will execute the READ operation or prepare for a WRITE operation. If the operation is READ, the Hybrid Transceiver will go read the specified register and prepare to return the value to the SPI Master. If the operation is a WRITE, the Hybrid Transceiver will accept the second byte as the new Data value for the specified register.

#### SPI WRITE Sequence

Command sequence (SIN): OP CODE/REG, WDATA, NULL. Response sequence (SOUT): NULL, OP CODE/REG, WDATA (echo the OP CODE/REG and WDATA values).

#### SPI READ Sequence

Command sequence (SIN): OP CODE/REG, NULL, NULL. Response sequence (SOUT): NULL, OP CODE/REG, RDATA (echo the OP CODE/REG and then return the read RDATA value).

Connectivity for Business Critical Continuity

### **SPI Chip Select**

Upon completion of the READ or WRITE operation, the SPI Master must raise the SPI Chip Select (SCSX = 1). For multiple sequential read or write operations, it is required that the SPI Master must raise Chip Select (SCSX = 1) before starting the next SPI transfer. A minimum of 1 SPI clock period is required between sequential SPI operations. The Hybrid Transceiver will ignore all activity on the SCLK and SIN signals when SPI Chip Select is false (SCSX = 1). The SCLK signal may run continuously as in the case of multiple SPI slave devices, but this is not required. The SCLK signal is only sampled by the Hybrid Transceiver when SPI Chip Select is true (SCSX = 0).

#### **SPI Clock**

All SIN bits are clocked by the falling edge of SCLK and sampled by the Hybrid Transceiver on the rising edge of SCLK. All SOUT bits are shifted out of the Hybrid Transceiver on the falling edge SCLK and are stable (sampled) on the next falling edge SCLK. Refer to the SPI port detail timing diagram for further clarification. The last bit shifted out on a READ operation is driven on the SOUT line until the SPI Chip Select is driven false (SCSX = 1). After shifting out the last bit (on falling edge clock), all further SCLK cycles are ignored until the SCSX is raised and again lowered to start a new WRITE or READ transaction.

### SPI Clock Phase Detail

#### Notes:

- 1. SPI Clock (SCLK) shift data on falling edge, sample on rising edge.

- 2. Single byte transfer shown. Actual transfer requires SCSX to remain low for all 3 bytes.

- 3. SOUT is driven by the Hybrid Transceiver until the removal of SCSX. See detailed timing diagrams.

Connectivity for Business Critical Continuity

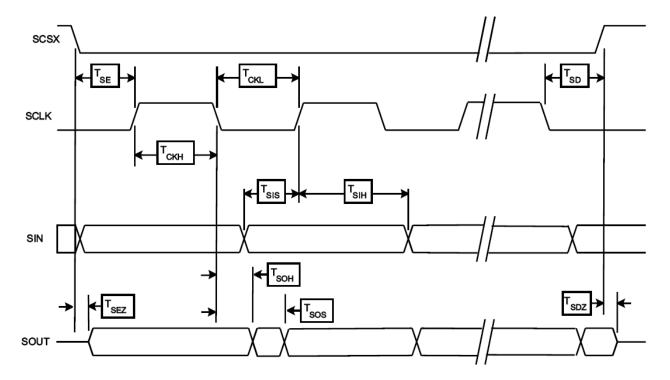

### **SPI Timing Detail**

#### **SPI Timing Detail**

| SITTING Detail   | -                                            |       |     |      |

|------------------|----------------------------------------------|-------|-----|------|

| Parameter        | Description                                  | MIN   | MAX | Unit |

| SCLK             | SPI Transfer rate                            | 0.100 | 2.0 | MHz  |

| T <sub>se</sub>  | SCSX falling to first edge SCLK              | 83    |     | ns   |

| T <sub>sD</sub>  | Last SCLK edge to SCSX rising                | 83    |     | ns   |

| T <sub>SEZ</sub> | SCSX falling edge to SOUT valid              |       | 167 | ns   |

| T <sub>SDZ</sub> | SCSX rising edge to SOUT High-Z              |       | 167 | ns   |

| Т <sub>скн</sub> | SCLK High time                               | 208   |     | ns   |

| T <sub>CKL</sub> | SCLK Low time                                | 208   |     | ns   |

| T <sub>SIS</sub> | SIN set-up, data valid to SCLK rising edge   | 83    |     | ns   |

| T <sub>SIH</sub> | SIN hold, SCLK rising edge to SIN change     | 83    |     | ns   |

| Т <sub>зон</sub> | SOUT hold, SCLK falling edge to SOUT change  |       | 167 | ns   |

| T <sub>sos</sub> | SOUT set-up, SCLK falling edge to SOUT valid |       | 292 | ns   |

| SCSX High        | SCSX High Time between sequential transfers  | 40    |     | ns   |

### SPI Transfer Sequence Examples

### **SPI WRITE Operation**

Connectivity for

**Business Critical Continuity**

#### Notes:

- 1. SCLK may run continuously, as in the case of multiple SPI slave devices.

- 2. SIN Data is sampled on the rising edge SCLK.

- 3. SOUT Data is shifted on the falling edge of SCLK.

- 4. All clocks and data outside of SCSX=0 are ignored.

- 5. The SCSX signal must toggle for at least one SCLK cycle between sequential SPI READ or WRITE operations.

Connectivity for Business Critical Continuity

### SPI Registers – S/W Control

| Register             | Symbol                                       | Read/Write | Description                                                                                                                                                                                                       |  |

|----------------------|----------------------------------------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0 through 7          | MFG_ID                                       | R          | 8 byte Manufacturer ID = "STLW FL"                                                                                                                                                                                |  |

| 10                   | PROD_ID                                      | R          | Product ID =<br>i.e. 0x01 for HTP-TR4-S001<br>0x02 for HTP-TR4-S002<br>0x03 for HTP-TR4-S003, etc.                                                                                                                |  |

| 11                   | REV_ID                                       | R          | Microcode Revision ID                                                                                                                                                                                             |  |

| 12<br>13             | DATE_CODE1<br>DATE_CODE0                     | R          | Date Code MSByte, i.e. 0407 = 4 <sup>th</sup> week, 2007<br>Date Code LSByte                                                                                                                                      |  |

| 14<br>15<br>16<br>17 | USER_ID3<br>USER_ID2<br>USER_ID1<br>USER_ID0 | R/W        | 32 bit storage for User programmable values                                                                                                                                                                       |  |

| 20<br>21<br>22<br>23 | IDET0<br>IDET1<br>IDET2<br>IDET3             | R          | RSSI for Channel 0, 1, 2, 3. Signed 8 bit value.<br>Resolution: 1 bit = 0.5dBm<br>Range = -21dBm to -2dBm<br>i.e21dBm = 0xD6 and -2dBm = 0xFC                                                                     |  |

| 24                   | TEMPSENS                                     | R          | Thermal sense for optical die, Signed 8 bit value.<br>Resolution = 1 bit / °C<br>Range = -50C to +90C                                                                                                             |  |

| 25                   | RXEN                                         | R/W        | RX Channel Enable, 1=Enable, 0=Disable<br>Also requires RXEN H/W pin driven true.<br>Power-up Default = 0x0F<br>b3 = RX Chan 3 Enable<br>b2 = RX Chan 2 Enable<br>b1 = RX Chan 1 Enable<br>b0 = RX Chan 0 Enable  |  |

| 26                   | RXSD                                         | R          | RX Signal Detect, 1=Modulated Optical Signal Present, 0=Not Present<br>b3 = RX Chan 3 SD<br>b2 = RX Chan 2 SD<br>b1 = RX Chan 1 SD<br>b0 = RX Chan 0 SD                                                           |  |

| 34                   | TXEN                                         | R/W        | TX Channel Enable. 1=Enable, 0=Disable<br>Also requires TXEN H/W pin driven true.<br>Power-up Default = 0x0F.<br>b3 = TX Chan 3 Enable<br>b2 = TX Chan 2 Enable<br>b1 = TX Chan 1 Enable<br>b0 = TX Chan 0 Enable |  |

Connectivity for Business Critical Continuity

### SPI Registers – Continued

| Register | Symbol  | Read/Write | Description                                                                                                                                                                                                                                                                                                                                                                               |

|----------|---------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 35       | TXSD    | R          | TX Signal Detect, 1=CML Signal Present, 0=Not Present<br>b3 = TX Chan 3 SD<br>b2 = TX Chan 2 SD<br>b1 = TX Chan 1 SD<br>b0 = TX Chan 0 SD                                                                                                                                                                                                                                                 |

| 36       | TXFAULT | R          | TX Fault Status (1=Fault, 0=No Fault)<br>b7 = Latched TX Fault Chan 3, reset on READ<br>b6 = Latched TX Fault Chan 2, reset on READ<br>b5 = Latched TX Fault Chan 1, reset on READ<br>b4 = Latched TX Fault Chan 0, reset on READ<br>b3 = TX Fault Chan 3 (not latched)<br>b2 = TX Fault Chan 2 (not latched)<br>b1 = TX Fault Chan 1 (not latched)<br>b0 = TX Fault Chan 0 (not latched) |

| 40       | SELFTST | R/W        | Self Test Control, 1=Initiate, 0=Skip<br>b4 = Self Test complete (1=done, 0=not yet done)<br>b0 through b3 = Any non-zero value initiates self test.                                                                                                                                                                                                                                      |

| 41       | SELFSTS | R          | Self Test Status,<br>0x00 = FAIL<br>0x0F = PASS                                                                                                                                                                                                                                                                                                                                           |

Notes:

- 1. All undefined or skipped registers are reserved for future expansion, and SPI writes should not be performed to these locations.

- 2. The TXEN and RXEN H/W pin can be used to enable/disable all channels via hardware. Individual control of each channel is accomplished via the SPI registers. The H/W pin and SPI register settings are logic ANDed to create the individual channel control.

- 3. The test requires up to 100msec to complete. At the end of the test, the b4 is set in SELFTST register to indicate test completion and valid status is ready in SELFTST register. The read-back value for b3-b0 of SELFTST is always a 0.

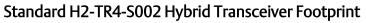

Ordering Options

| Part Number   | Name                     | Description                                                         |

|---------------|--------------------------|---------------------------------------------------------------------|

| H2-TR4-SKT-R3 | BGA Socket               | 16x16 BGA surface mount socket, no clip                             |

| H2-TR4-CLP-R3 | BGA Socket with Clip     | 16x16 BGA surface mount socket with integrated clip                 |

| H2-TR4-S001   | Standard Hybrid          | Hybrid Transceiver, 1" fiber length from feedthrough exit, straight |

|               | Transceiver – Option 001 | fiber route configuration.                                          |

| H2-TR4-S002   | Standard Hybrid          | Hybrid Transceiver, 6" fiber length from feedthrough exit, straight |

|               | Transceiver – Option 002 | fiber route configuration.                                          |

| H2-TR4-Sxxx   | Hybrid Transceiver       | The –Sxxx suffix represents unique part numbering for fiber route   |

|               |                          | and termini options. Consult the factory for details and for custom |

|               |                          | part numbering for your application.                                |

| H2-TR4-PULL   | Extraction Tool          | Tool to aid in removing the Hybrid Transceiver from the BGA         |

|               |                          | socket.                                                             |

| H2-TR4-PIN    | Pin Straightening Tool   | Tool to aid in straightening the pins of the Hybrid Transceiver.    |

| H2-TR4-EVAL   | HTP EVAL Card            | Demonstration and evaluation card, includes support hardware,       |

|               |                          | BGA Socket, and the Hybrid Transceiver.                             |

Connectivity for

**Business Critical Continuity**

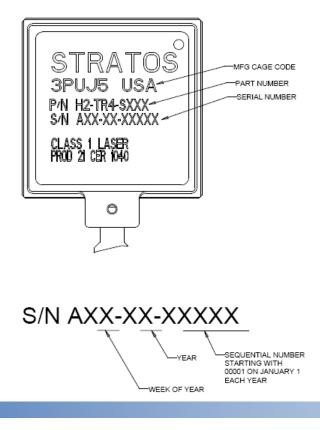

### H2-TR4-Sxxx Hybrid Transceiver Label

Connectivity for Business Critical Continuity

### H2-TR4-SKT-R3 Mechanical Detail

**Stratos** Connectivity Solutions

All dimensions are in inches.

Connectivity for Business Critical Continuity

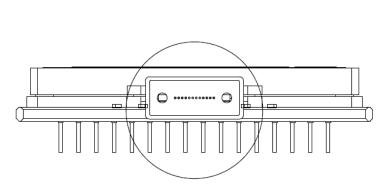

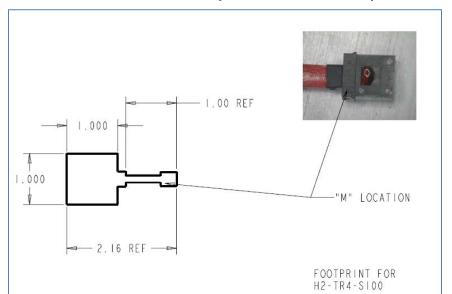

### Standard H2-TR4-S001 Hybrid Transceiver Footprint

All dimensions are in inches.

| Stratos<br>H2-TR4-Sxxx<br>Hybrid Technology Quad Op                                                                                                                                             | otical Transceiver                                                                                                | Connectivity for<br>Business Critical Continuity |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|

| Hybrid Q                                                                                                                                                                                        | onnectivity Solutions – Stratos Po<br>Quad Optical Transceiver Worksl<br>Theet to specify your order for Hybrid T | heet                                             |

| Customer, Program:                                                                                                                                                                              |                                                                                                                   |                                                  |

| Data Rate:                                                                                                                                                                                      |                                                                                                                   |                                                  |

| Fiber Type:                                                                                                                                                                                     | <ul> <li>50/125 μm Graded Index Multin</li> <li>Effective Modal Bandwidth</li> <li>Other:</li> </ul>              | mode: Corning OM4 4700 MHz-km                    |

| <b>Straight or Shuffle Route:</b><br>(If shuffle route then provide Pin# vs Rx,Tx mapping)                                                                                                      |                                                                                                                   |                                                  |

| <b>Pigtail Length:</b> (+/- 0.5 inches is default)<br>(If complex routing then provide step file)<br><b>Special Notes:</b> (Boot color, heatshrink, labels,<br>special testing, shipping, etc.) |                                                                                                                   |                                                  |

| <b>Part Number:</b><br>(Assigned by Emerson Connectivity Solutions)                                                                                                                             | Assigned By:                                                                                                      | Date:                                            |

Connectivity for Business Critical Continuity

#### IMPORTANT NOTICE

Emerson Connectivity Solutions product line, Stratos reserves the right to make changes to or discontinue any optical link product or service identified in this publication, without notice. Stratos recommends that its customers obtain the latest version of the publications to verify, before placing orders, that the information being relied on is current. Stratos warrants performance of its optical link products to current specifications in accordance with the Stratos standard warranty. Testing and other quality control techniques are utilized to the extent that Stratos has determined it to be necessary to support this warranty. Specific testing of all parameters of each optical link product is not necessarily performed on all optical link products. Stratos products are not designed for use in life support appliances, devices, or systems where malfunction of a Stratos International, Inc. product can reasonably be expected to result in a personal injury. Stratos customers using or selling optical link products for use in such applications do so at their own risk and agree to fully indemnify Stratos for any damages resulting from such improper use or sale. Stratos assumes no liability for Stratos applications assistance, customer product design, software performance, or infringement of patents or services described here in. Nor does Stratos warrant or represent that a license, either expressed or implied is granted under any patent right, copyright, or intellectual property right, and makes no representations or warranties that these products are free from patent, copyright, or intellectual property right, and makes no representations or warranties that these products are for illustrative purposes only. Stratos makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

| <b>Emerson Network Power</b><br>The leader in enabling<br>Business-Critical Continuitv.                        | <ul> <li>AC Power Systems</li> <li>Connectivity</li> <li>DC Power Systems</li> </ul>                                       | <ul> <li>Embedded Power</li> <li>Inbound Power</li> <li>Integrated Cabinet Solutions</li> </ul> | <ul> <li>Outside Plant</li> <li>Precision Cooling</li> <li>Site Monitoring and Services</li> </ul>                      |

|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| Emerson Network Power<br>Connectivity Solutions<br>Stratos<br>1333 Gateway Dr., Ste 107<br>Melbourne, FL 32901 | Emerson Network Power<br>Connectivity Solutions<br>USA Headquarters<br>3000 Lakeside Dr, Ste 308N<br>Bannockburn, IL 60015 |                                                                                                 | Emerson Network Power and the<br>Network Power logos are<br>service marks of Emerson Electric<br>©2011 Emerson Electric |

For product Information: www.EmersonConnectivity.com or call 321.308.4100 For product Information: call 507.833.8822 or 800.247.8256